Silicon Chip Design & Semiconductor Engineering

Building the chips of tomorrow

CONTACT US

certificate Description

Learn next-level VLSI design skills for top Silicon Valley companies

UCSC Silicon Valley Extension Silicon Chip Design & Semiconductor Engineering professional certificate program provides students with the core design skills they need to work at top companies in the Valley. Both established and aspiring engineers develop new skills, gain insight into digital and analog design techniques and methodologies, and learn from our expert faculty.

Integrated circuit curriculum

You'll explore ASIC, semiconductor, EDA, device, and integrated circuits. In our VLSI lab, our instructors will give you the opportunity to get hands-on experience with hardware specification, logic design, verification, synthesis, physical implementation, circuit design, integrated circuit product testing, and the latest EDA tools on Linux.

Who are our students?

Logic designers, design for test professionals, verification engineers, and project leaders receive next-level training for career growth so they can meet the latest demands of top Silicon Valley employers.

Two tailored elective tracks

- Track 1: Front-end Design

For professionals pursuing careers in application-specific integrated circuits (ASIC) architectural definitions and logic designs for its implementation. - Track 2: Back-end Design

For professionals interested in the physical implementations of ASIC designs from synthesis to silicon.

Silicon Chip Design & Semiconductor Engineering certificate program objectives

- Implement Verilog modeling of digital logic

- Write assertions for formal verification using SystemVerilog

- Build an advanced UVM verification environment

- Understand and implement DFT concepts in an ASIC design

- Complete practical designs with Xilinx FPGAs

- Implement a design from RTL to GDS

Access to premier tools

Using premier industry tools from Cadence, OpenROAD, Siemens, and Synopsys, you’ll learn front-end and back-end ASIC design and leave the classroom ready to apply new skills at your job.

Silicon Chip Design: A Growing Opportunity

Despite restricted hiring in many tech areas these days, the demand for skilled silicon chip design engineers is blossoming. Learn about the job outlook for VLSI chip designers, in particular, jobs involving microelectronic devices, such as microprocessors and memory chips, and skills to build a competitive resume. (JANUARY • 2023)

Program Overview

Estimated Cost: $4,350–$5,500 + est. course materials: $500 (You pay only for courses you enroll in.) | International Tuition Cost

Program Requirements: 5 courses (minimum 14 quarter units). Take 3 required courses (9 quarter units) and 2 elective courses (minimum 6 quarter units). End with certificate of completion review.

Minimum Hours of Instruction: Minimum 150 hours of instruction.

Estimated Duration: A full-time student can complete the certificate in 9–12 months.

Courses

1. Core Course(s): (Choose Three)

2. Electives: Front-End

3. Electives: Back-End

4. Completion Review:

5. Related Workshops - not for credit

Meet Our Instructors

Certificate Inquiry Form

Recommended Course Sequence

Beginners should take introductory courses before advanced. Other courses can be taken based on your interests and professional levels.

Related Electives

- Embedded System Hardware Architectures, Introduction (3.0)

- System Design for Low Power Management (1.0)

Substitutions

Shared credits

Some Engineering and Technology courses may be listed in more than one program. However, only one course may be shared between two E&T certificate programs unless otherwise noted.

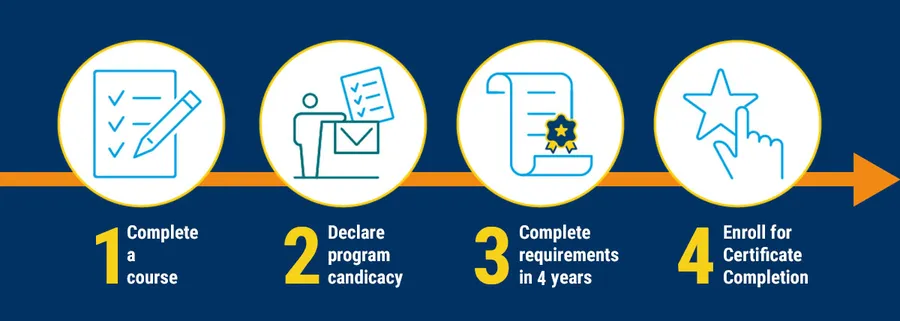

To receive your certificate

Requisite Knowledge

Technical expertise

You need a degree in a technical field or equivalent knowledge acquired through training and experience in hardware design and development. Experience with UNIX and/or LINUX is required for lab sessions. Knowledge of a programming language such as C, Perl or Bash Shell is helpful.

Please review course descriptions

Make sure you have taken necessary prerequisites or meet the requirements through job experience or previous education before registering for a course.

Advisory Board

Certificate Program Chair

ARVIND VIDYARTHI, M.S.E.E., ARVIND VIDYARTHI, M.S.E.E., senior director of silicon design implementation and methodology at Altera (an Intel company), has 20+ years of industry experience in chip implementation in various major semiconductor companies such as Sun Microsystems, AMD, and Nvidia. Learn more.

Certificate Program Advisory Committee

JEFFERY GOODING, MSEE

Account Technology Executive, Cadence Design Systems

SAM HUYNH, Ph.D., MSEE

Principal Member of Technical Staff, AMD

Instructor, Silicon Chip Design & Semiconductor Engineering Certificate Program, UCSC Silicon Valley Extension

JIM SCHULTZ, B.S.

Product Marketing Manager, Digital Design Implementation, Synopsys Inc.

MANDAR MUNISHWAR, B.E.

Formal Verification Engineer, Google

Instructor, Silicon Chip Design & Semiconductor Engineering Certificate Program, UCSC Silicon Valley Extension

JOSE RENAU, Ph.D.

Professor, Computer Science and Engineering, Jack Baskin School of Engineering, UC Santa Cruz

Consultant, Esperanto Technologies, Inc.

BENJAMIN TING, M.S.E.E.

Principal Engineer, Micron Technology

Instructor, Silicon Chip Design & Semiconductor Engineering Certificate Program, UCSC Silicon Valley Extension

Establish Candidacy

Grade Requirements

Please note that only letter grades of C or higher may be applied to a certificate, and in some programs, students may have more stringent requirements. Students in most employer- and government-sponsored payment programs, such as workforce development, as well as international students on F-1 visas, need to maintain a B average to meet their requirements.

See Grading and Credits Policy for further information.